FT600とFPGA間でデータの送受信を行いましたので、ご参考に手順をお示しします。

FT600は「Multi-Channel FIFO」と「245 Synchronous FIFO」というふたつの動作モードを選択できます。後者のほうがアプリケーションで確認すべき事項が少なそうですので、今回の実験では245 Synchronous FIFOモード(以後、245モード)使用しました。

FT600用API(D3XX)に関しては下記の資料を参考してください。

AN_379 - D3XX Programmers Guide

1.ハンドルの取得

FT_Create()によりハンドルを取得します。Flagは"FT_OPEN_FT60X_BY_INDEX"を使用しました。問題がなければ0(=FT_OK)が返ります。

FT_Create(&index, FT_OPEN_FT60X_BY_INDEX, &ftHandle);

2.チップ情報の取得

FT_GetChipConfiguration()により、Vendor ID(VID), Product ID(PID)など、チップの情報が正しく取得できるかを確かめます。

下図のように取得できました。VID,PIDがデータシートに示されているデフォルト値とあっている事が確認できます。

FIFOClock=0(CONFIGURATION_FIFO_CLK_100)なので100MHzが出力されています。

FT_60XCONFIGURATION chipConfig; FT_GetChipConfiguration(ftHandle, &chipConfig)

3.動作モードの変更(チップ情報の書き換え)

245FIFOモードで動作させるためにはFIFOModeを"FIFO_MODE_245"、ChannelConfigを"CHANNEL_CONFIG_1"としなければならないようです。

先に読み出したchipConfigを書き換えてFT_SetChipConfiguration()で書き込みます。

chipConfig.FIFOMode = CONFIGURATION_FIFO_MODE_245; chipConfig.ChannelConfig = CONFIGURATION_CHANNEL_CONFIG_1; FT_SetChipConfiguration(ftHandle, &chipConfig);

動作モードはGPIO[1..0]ピンを使用して設定もできるようですが、執筆時には確かめられていません。

4.データの送信 (FT600→FPGA)

FT_WritePipe()によりデータを送信します。第2引数のPipeIDには0x02を指定します。第6引数のOverlappedにはNULLを指定しておきます。

Overlapを使用すると非同期動作を行えます。つまりFT_WritePipe関数がデータの送信完了を待ちません。このときの返り値は"FT_IO_PENDING"となります。今回はNULLとしていますので送信完了まで関数から返りません。

FT_WritePipe(ftHandle, 0x02, buff, 10, &bytesTransferred, NULL);

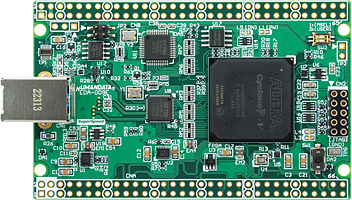

FPGA側での受信波形を示します。FT600から出力した"HuMANDATA*"という10ByteのデータをFPGAで正常に受信できています。

5.データの受信 (FPGA→FT600)

FT_ReadPipe()によりデータを受信します。第2引数のPipeIDには0x82を指定します(MSBが方向を示す)。第4引数には受信するバイト数を指定します。今回は4Byteを受信してみます。

受信待ちをするため、Overlapを使用しました。FT_ReadPipe()から"FT_IO_PENDING"が返った後、FT_GetOverlappedResult()により受信完了をポーリングします。

ftStatus = FT_ReadPipe(ftHandle, 0x82, buff, 4/*bytes*/, &bytesRead, &overlappedRead);

if(ftStatus == FT_IO_PENDING){

while(1){

ftStatus = FT_GetOverlappedResult(ftHandle, &overlappedRead, &bytesRead, FALSE);

if(ftStatus == FT_IO_INCOMPLETE){

continue;

}else if(ftStatus != FT_OK){

break;

}else{ //ftStatus == FT_OK

result = 0;

break;

}

}

}

TXE信号はFT600が受信可能である事を表す出力信号です。FT_ReadPipe()が実行される事でLowとなります。FPGAはTXEがLowであれば押しボタンからの入力(shot)でデータ出力を開始し、TXEのHighで停止します。

今回4Byteの受信を実行したので、4Byte(2Word)を受信した時点でFT600がTXEをHighとしています。

アプリケーションでは希望のデータ量を受信できたあとのFT_GetOverlappedResult()の実行でFT_OKが返ります。

4096Byteを受信した際の波形を下記に示します。

・全体

・2048Word

お問い合わせについて

弊社では、FPGAそのものの使い方、開発ツールの使い方などは、サポートしておりません。

[kw] 2015-10-09 EDA-009 FTDI USB3.0 FT600

[]